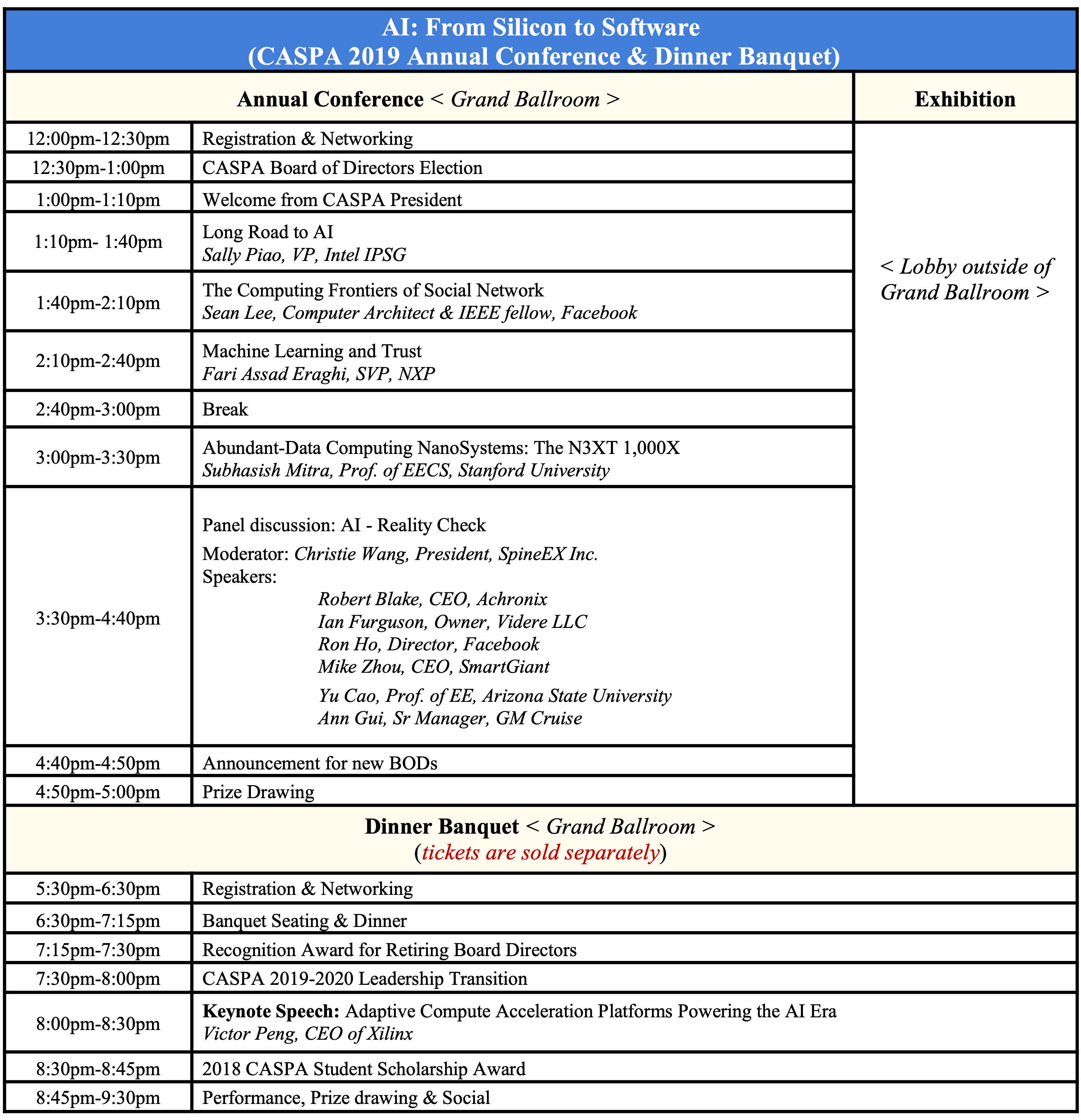

Date: Saturday, Oct. 19th, 2019

Venue: DoubleTree Hilton Hotel (39900 Balentine Drive, Newark, CA 94560)

Annual Conference Time: 12:00pm to 5:00pm (limited early bird free tickets)

Dinner Banquet Time: 5:30pm to 9:30pm (tickets are sold separately)

Speakers and Panelists Introduction

Dinner Banquet Keynote Speaker

Victor Peng

President and Chief Executive Officer, Xilinx, Inc.

Biography:

VICTOR PENG is President and Chief Executive Officer of Xilinx, Inc., and serves on the Board of Directors. Peng has more than 30 years of experience defining and delivering leadership technologies across FPGAs, SoCs, GPUs, high-performance microprocessors and chip sets, and microprocessor IP products.

Since becoming CEO of Xilinx in February of 2018, Peng has rolled out plans for a transformation to address new markets with new technology, underpinned by the Adaptive Compute Acceleration Platform (ACAP). In his previous role as Chief Operating Officer, Peng managed Global Sales, Product and Vertical Marketing, Product Development, and Global Operations and Quality. Prior to that, he served as Executive Vice President and General Manager of Products, where he led the definition, development, and product marketing of the company’s portfolio of products and differentiated technologies – resulting in three consecutive generations of core product leadership and significant industry breakouts in integration and programming.

Peng previously served as Corporate Vice President of the graphics products group (GPG) silicon engineering with AMD and was a leader for AMD’s central silicon engineering team supporting graphics, console game products, CPU chipset and consumer business units. Prior to that, Peng held executive and engineering leadership roles at TZero Technologies, MIPS Technologies, SGI and Digital Equipment Corp.

Peng holds four U.S. patents and serves on the Board of Directors of the Semiconductor Industry Association and KLA Corporation, a developer of industry-leading equipment and services for electronics industry. He earned a bachelor’s degree in electrical engineering from Rensselaer Polytechnic Institute and a master’s degree, also in electrical engineering, from Cornell University.

Xilinx develops highly flexible and adaptive processing platforms that enable rapid innovation across a variety of technologies – from the endpoint to the edge to the cloud. Xilinx is the inventor of the FPGA, hardware programmable SoCs and the ACAP, designed to deliver the most dynamic processor technology in the industry and enable the adaptable, intelligent and connected world of the future. Xilinx reported revenues of $3.06 billion for its fiscal year ending April 2019.

Speech Title: Adaptive Compute Acceleration Platforms Powering the AI Era

Abstract:

Technology that can process the staggering amounts of data being generating at the edge and in the cloud in close to real-time is enabling achievements once thought impossible and will have a profound impact on people’s daily lives. Artificial Intelligence is playing an ever-increasing role and is driving the emergence of new architectures and applications at an unprecedented pace. Adaptive Compute Acceleration Platforms (ACAPs) enable a diversity of Domain Specific Accelerators (DSA’s) to be developed and rapidly deployed for end point, edge, and cloud applications. Xilinx’s Versal is the industry’s first ACAP. Its heterogenous architecture delivers factors of performance improvement over traditional processors for a wide range of applications including AI. The new Artificial Intelligence Engine (AIE) integrated in Versal is a hardware adaptable spatial processing engine that delivers world-leading AI inference performance. Versal together with a new powerful development environment will accelerate the era of pervasive AI.

Annual Conference Speakers

AC Speaker 1:

Sally Piao

VP, Intel IPSG

Biography:

Sally H. Piao is a vice president in the Infrastructure and Platform Solutions Group and director of debug capabilities at Intel Corporation. She leads the team responsible for the delivery of mission critical debug hardware and software across the Intel roadmap.

An expert in software development and global management with over 25 years of industry experience, Piao joined Intel in 2018. Prior, she was vice president of database and Exadata system testing and vendor certification at Oracle Corporation. Earlier in her career, she worked as an application developer in and held a number of various leadership positions at Oracle, including vice president of development. During her tenure, she managed a large international team across the United States, India, China, and Ireland.

For over 15 years, Piao specialized in large scale systems simulation and testing, making major contributions to many of Oracle’s product release, including the Oracle Database, Fusion Middleware, Fusion Applications, Exadata, and the Oracle Public Cloud.

A dedicated philanthropist, Piao has served as a board member and coach for Odyssey of the Mind and in various roles with Young Men’s Service League.

She holds a bachelor’s degree in electrical engineering from the University of Science and Technology of China and a master’s degree in electrical engineering from the California Institute of Technology. She also received Oracle’s Advanced Executive Initiative business training from IESE Business School and the Stephen M. Ross School of Business at the University of Michigan.

Speech Title: Long Road to AI

Abstract:

The vision of AI is grand and daunting. Its life changing and revolutionary forecast has caused much excitement and social concern. But how far are we from that vision? How should we prepare to take advantage of the bleeding edge technology? The talk will share some real world examples of the excruciatingly painful path towards realizing AI.

AC Speaker 2:

Hsien-Hsin Sean Lee, Ph.D.

Head of AI Infrastructure Research, Facebook Boston

Biography

Hsien-Hsin Sean Lee leads the AI Infrastructure Research group at Facebook Boston. Previously, he directed the EDA design flow solutions and oversaw the entire PDK development for IC design customers at Taiwan Semiconductor Manufacturing Co. (TSMC), Taiwan. Prior to TSMC, he was a tenured Associate Professor at the School of Electrical and Computer Engineering, Georgia Tech at Atlanta for 10 years, and spent one year as an Architecture Manager at Agere Systems and six years as a senior CPU architect at Intel Corporation. Dr. Lee holds a Ph.D. in Computer Science and Engineering from the University of Michigan at Ann Arbor. He received National Awards including the NSF CAREER Award and the Department of Energy Early CAREER Award. He has published two book chapters and more than 100 technical articles including 4 Best Paper Awards and one 10-year most influential paper award. He served as an Associate Editor of IEEE Trans. on Computers, IEEE Trans. on CAD, ACM Trans. on Architecture and Code Optimization, and IEEE MICRO Magazine. He also served as the General Chair for IISWC 2010, the Program Co-Chair for MICRO 2016, an Executive Committee Member for IEEE-TCCA, an Industry Advisory Board Member for IEEE Computer Society and a TPC Member for more than 90 international conferences. Dr. Lee holds 24 US patents and is a Fellow of the IEEE.

Speech Title: The Computing Frontiers of Social Network

Abstract

Social networks have been deeply woven into our everyday life. These platforms host a plethora of real-time services to keep people connected, provide useful/customized information, and maintain information transparency. Underneath their infrastructure, the adoption of AI/Machine Learning (ML) techniques is rapidly becoming omnipresent in both datacenters and end users’ devices, steering a rich feature set to enhance the effectiveness of users’ communication and to improve the quality of online social experiences. Meanwhile, to achieve these objectives, ML can consume enormous computing resources and require meticulous resource design, provisioning, and management. In this talk, I will share Facebook’s perspectives on the novel challenges and forward-looking technologies in social network computing, in particular, their implication to future end-to-end system designs. In addition, I will discuss our open-source framework endeavor such as PyTorch as well as our joint effort with other ML enthusiasts in standardizing ML benchmarks for the global research community.

AC Speaker 3

Fari Assad-Eraghi

SVP,NXP

Biography:

Fari Assad-Eraghi is Senior VP of Innovation and Advanced Technologies at NXP. He is responsible for technical roadmaps in all product and technology areas spanning computing, connectivity, AMS, and security. Prior to this role, he was CTO of IoT and Security, a Business Unit with $4B annual revenue. Among other responsibilities, he and his team set the roadmap and delivered security architecture and IP for NXP. Before joining NXP in 2016, he was VP of Advanced Technology at InvenSense. There he was tasked with expanding company’s product portfolio beyond inertial sensors to audio solutions, ultrasonic fingerprint sensors, and health sensors. Fari earned his M.S. and Ph.D. degrees in EECS from UC Berkeley. From 1995 to 2001 he was with IBM TJ Watson Research Center where he contributed to development of first commercial version of CMOS SOI for VLSI. At Rambus he and his teams developed high speed data communication circuits and systems, including the Terabyte/sec signaling initiative. As Senior VP of Engineering and Operations at SiTime, he led the first commercialization of MEMS-based timing products.

Fari has contributed to a wide technical area spanning semiconductor device physics, transducers, circuit design for analog and mixed-signal, low-power computing, and security. He has given numerous invited talks including at VLSI Symposium, CICC, RFIC, ISLPED, SOI, S3S and SDW Conferences. He is on IEEE’s North America and Europe Executive Committee. Dr. Assad-Eraghi has contributed to more than 100 technical papers, including the best paper at 2016 ISSCC, and has 70 issued patents.

Speech Title:Machine Learning and Trust

Abstract:

Machine Learning capabilities have been growing tremendously over the past 10 years due to advances in Deep Learning algorithms, acceleration of computational capabilities (both at cloud and edge), and availability of enormous amount of data. This has brought about many beneficial applications from speech recognition and machine translation to image and facial recognition. Countless other applications are being developed that will have a seminal impact on the entire human society. ML will transform all aspects of economy from healthcare (diagnostics, disease control, pharmaceuticals), to infrastructure (transport, logistics, energy), to finance, to advanced industries, and clearly to consumer. This realization has not only led to break-neck advances in computer science, software and algorithms, but also a renaissance in hardware innovations that address both processing and storage of data. Vast engineering resources have been directed towards improving performance and power efficiency of algorithms and their silicon counterparts. The efforts have been directed to both ends of the spectrum, from massive data centers consuming Mega-Watts of power and computing 100’s of petaflops, to end node IoT devices with milli-Watt power consumption and a few MIPS of compute resources. In this race for performance, until recently little attention was paid to the trust facet of Machine Learning. If any, the focus was only on improving accuracy of ML models. However, with the broad reach of ML finally being appreciated, many trust aspects are gaining attention and a burgeoning research field is taking shape. The Trust Umbrella covers security, privacy, interpretability, and fairness of ML. ML and security intersect in two ways: ML for security and security of ML. ML can be utilized to impact security of platforms and applications. It can enhance security as an additional defense mechanism by enabling tasks such as anomaly detection, intrusion detection, and control flow protection.

On the other hand, it can become a tool of bad actors by making exploitation of system vulnerabilities such as ‘side-channel attacks’ easier and more automated. Security of ML itself is however the larger concern. Both in the training phase and inferencing phase, researchers have shown that ML can be exploited. In training phase, data poisoning can lead to ML models that have specific vulnerabilities and ‘back doors’. In inferencing phase use of adversarial inputs can intentionally cause ML to mis-predict, compromising security and safety. Although recent research papers have demonstrated exploitation of ML vulnerabilities, and also countermeasures against these attacks, the practical nature and real-world applicability of these investigations are in question. Therefore, the threat models need to be much better defined and systematic methods for evaluating effectiveness of countermeasures developed.

Under this Trust Umbrella the other factor to consider is model confidentiality. Given the disproportionate amount of resources spent into training the models, and the enormous curated data that is essentially embedded in these models, model confidentiality is of prime importance. The motivation is not only avoidance of IP loss, but also the realization that attacks against ML become more efficient if adversaries have “white-box” access to the models. Another important factor is data confidentiality. Data used both in training phase and inferencing phase can be sensitive, particularly in Machine Learning as a Service (MLaaS) applications. Examples include health, financial, industrial, and governmental data. If private data is leaked, it can lead to regulatory compliance violations (e.g., GDPR), loss of customer trust, and damage to a company’s brand. Recently, several advances in privacy-preserving ML have been made that rely on cryptographic techniques. They span from fully-homomorphic encryption (FHE), to HE and garbled circuits and multi- party compute techniques. All these approaches have significant computational overhead and are mostly limited to inferencing phase at this point. The field is very nascent and rapid advances in hardware and algorithms are being made. Finally, a major disadvantage of current machine learning approaches is that insights about the data and the task the machine solves is hidden in increasingly complex models. If one focuses only on performance, the result is more and more opaque models. For example, the winning models of the recent Kaggle.com competition were mostly ensembles of models or very complex models such as boosted trees or deep neural networks. Interpretability is the degree to which a human can understand the cause of a ML decision. With more opaque and complex models, interpretability becomes extremely difficult. This is a major issue once we realize that ML can be used for many tasks where fairness and lack of bias are important such as credit rating, and policing, or where wrong decisions can have safety consequences. We are at the very early stages of evaluating ML models from this perspective and developing interpretable models.

AC Speaker 4

Professor Subhasish Mitra

EECS, Stanford University

Biography:

Subhasish Mitra is Professor of Electrical Engineering and of Computer Science at Stanford University. He directs the Stanford Robust Systems Group, co-leads the Computation focus area of the Stanford SystemX Alliance, and is a faculty member of the Wu Tsai Neurosciences Institute. Prof. Mitra also holds the Carnot Chair of Excellence in NanoSystems at CEA-LETI in Grenoble, France. His research ranges across robust computing, NanoSystems, Electronic Design Automation, and neurosciences. Results from his research group have been widely deployed by industry and have inspired significant development efforts by government and research organizations in multiple countries.

Jointly with his students and collaborators, Prof. Mitra demonstrated the first carbon nanotube computer and the first three-dimensional NanoSystem with computation immersed in data storage. These demonstrations received wide-spread recognition: cover of NATURE, Research Highlight to the United States Congress by the National Science Foundation, and highlight as “important, scientific breakthrough” by news organizations around the world.

In the field of robust computing, Prof. Mitra and his students created key approaches for soft error resilience, circuit failure prediction, on-line self-test and diagnostics, and QED (Quick Error Detection) design verification and system validation. His earlier work on X-Compact test compression at Intel Corporation has proven essential to cost-effective manufacturing and high-quality testing of almost all electronic systems across the industry. X-Compact and its derivatives have been implemented in widely-used commercial Electronic Design Automation tools.

Prof. Mitra’s honors include the ACM SIGDA / IEEE CEDA Newton Technical Impact Award in Electronic Design Automation (a test of time honor), the Semiconductor Research Corporation’s Technical Excellence Award (for innovation that significantly enhances the semiconductor industry), the Intel Achievement Award (Intel’s highest corporate honor), and the United States Presidential Early Career Award for Scientists and Engineers from the White House. He and his students have published award-winning papers at major venues: ACM/IEEE Design Automation Conference, IEEE International Solid-State Circuits Conference, ACM/IEEE International Conference on Computer-Aided Design, IEEE International Test Conference, IEEE Transactions on CAD, IEEE VLSI Test Symposium, and the Symposium on VLSI Technology. At Stanford, he has been honored several times by graduating seniors “for being important to them during their time at Stanford.”

Prof. Mitra has served on the Defense Advanced Research Projects Agency’s (DARPA) Information Science and Technology Board as an invited member. He is a Fellow of the Association for Computing Machinery (ACM) and the Institute of Electrical and Electronics Engineers (IEEE).

Speech Title: Abundant-Data Computing NanoSystems: The N3XT 1,000X

Abstract

The world’s appetite for analyzing massive amounts of data (streaming video and audio, natural languages, real-time sensor readings, contextual environments or even brain signals) is growing dramatically. The computation demands of these abundant-data applications, such as machine learning, far exceed the capabilities of today’s computing systems, and can no longer be met by isolated improvements in transistor technologies, memories or integrated circuit architectures alone. To achieve unprecedented functionality, speed and energy efficiency, one must create transformative NanoSystems which exploit unique properties of underlying nanotechnologies to implement new architectures.

This talk will present the N3XT (Nano-Engineered Computing Systems Technology) approach that enables such NanoSystems through: (i) new computing system architectures leveraging emerging device (logic and memory) nanotechnologies and their dense 3D integration with fine-grained connectivity for computation immersed in memory, (ii) new logic devices (such as carbon nanotube field-effect transistors for implementing high-speed and low-energy logic circuits) as well as high-density non-volatile memory (such as resistive RAM that can store multiple bits inside each memory cell), amenable to (iii) ultra-dense (monolithic) 3D integration of thin layers of logic and memory devices that are fabricated at a low temperature.

A wide variety of N3XT hardware prototypes (built in research facilities and also in US foundry as part of DARPA’s 3DSoC program) represent leading examples of transforming scientifically-interesting nanomaterials and nanodevices into actual NanoSystems. N3XT NanoSystems target 1,000X system-level energy-delay product benefits especially for abundant-data applications. Such massive benefits enable a wide range of applications that push new frontiers, from deeply-embedded computing systems all the way to the cloud.

PanelDiscussion: AI – Reality Check

Panel Moderator: Christie Wang

President, SpineEX, Inc

Biography:

Christie Wang is a serial entrepreneur and investor in the medical device field. She co-founded and invested in a couple of innovative medtech companies including products such as non-invasive glucose monitoring system and an orthopedics company which developed innovative interbody implants and AI enabled spine surgical robots in spinal fusion surgeries. Prior, Christie was CEO of Unisource Inc. (USA), a cross-border venture firm and industrial platform supported by Jiangsu Province, PRC and its leading enterprises, and was empowering innovative smart healthcare and medtech technology in their Asia/China entry endeavors. Before that, she worked for Hewlett Packard Legal Department in investments, corporate and intellectual property. Christie is experienced in medical product application design using bio-sensors and predictive analysis, contracted manufacturing, regulatory certifications, licensing and IP, and in particular medtech investment, M&A and capital markets in US and Asia.

Meanwhile, Christie invested and consulted a few innovative medical device/pharma companies in their product development, financing, regulatory and market entry endeavors. Christie studied at Northwestern University School of Law (J.D.) and Kellogg MBA Program, and graduated from the Northwestern Medical Innovation Program.

Christie was appointed Chair of Library Commission, City of Cupertino (home of Apple Company), California in 2017. She served as mentor for Stanford University Technology Innovation. Christie was awarded the Most Outstanding Overseas Youth Chinese by the State Council of PRC in 2015 and met with Chinese President Xi Jinping in Seattle.

Panelist 1

Robert Blake

President and CEO, Achronix

Biography: Robert Blake has worked in the semiconductor industry for more than 25 years. Prior to Achronix Semiconductor, he was the Chief Executive Officer of Octasic Semiconductor based in Montreal, Canada. Mr. Black worked at Altera in a variety of sales, marketing and general management roles. As Vice President of Product Planning, he was responsible for defining Altera’s programmable logic products solutions. He has been developing ASIC and programmable logic for high speed telecom and network applications for more than 17 years. Prior to Altera, he worked as LSI logic and Fairchild where he developed ASIC technology. He holds a Master in Engineering and in Business and Microelectronics and Bachelor of Science in Applied Physics and Electronics from University of Durham in England.

Panelist 2

Ian Ferguson

Owner, Videre LLC

Biography:

Ian Ferguson runs a consulting business which has touched a number of aspects of Artificial Intelligence/Machine learning including

– Defining the go-to-market strategy for a company focused on automating inventory counting in warehouses using drones

– Creating Recurrent Neural Network (RNN) solutions focused on speech workloads in data center

– Supporting fund raising activities for a software company in the autonomous vehicle spac

Prior to working at PINC, Ian worked for nearly eleven years at Arm. Ian held a number of roles including

- Creating a partner ecosystem around Arm’s formative software business now referred to as the Pelion platform

- VP of corporate marketing and strategic alliances, a group which led Arm’s engagement with strategic software partners like Google, Microsoft and Ali Baba

- VP of segment marketing, a team which created demand for Arm technology across a range of applications including phones, industrial IoT, networking and automotive

- Established, defined and implemented the server initiative

Prior to Arm, Ian held various business development and product marketing roles for Enigma Semiconductor (a start-up creating network switch chipsets), QuickLogic, IDT and Motorola Semiconductor (which became Freescale). Ian has a degree in Electrical and Electronics Engineering from Loughborough University.

Panelist 3

Ron Ho

Director, Facebook

Biography:

Dr. Ron Ho started his career at Intel in the early 1990s, working on the 486, Pentium, Pentium II, and Itanium III processors over a ten-year period. He spent a second decade at Sun Microsystems and later Oracle, developing on- and off-chip IO technologies as well as DRAM-centric workload accelerators. In 2014 he went to Altera (later Intel) to play with off-chip transceivers — serdes, DDR, and 2.5D IOs — and shipped these with 20nm and 14nm FPGAs. In 2018 he moved to Facebook, where he is currently Director of Silicon Engineering, focusing on custom silicon chips for Augmented and Virtual Reality. Ron earned his Ph.D. from Stanford University.

Panelist 4

Mike Zhou

Founder, President and CEO of SmartGiant Technology Co. Ltd.

Biography:

Mr. Mike Zhou has 21 years of experience in the semiconductor industry. He is founder, President and CEO of SmartGiant Technology Co. Ltd., which has been very successful in the field of automated testing and industrial artificial intelligence since founded 14 years ago. The company excelled in the filed with multiple patents and a portfolio of products. Before SmartGiant, Mr. Zhou was senior engineering manager at Gaoke Communications Technologies Corp., focusing on designing telecommunication network access systems and developing multi-service communication platforms. Prior to that, Mr. Zhou was an engineer at Midea Group, developing home appliances controllers. Mr. Zhou earned his M.Eng. degree from Sun Yat-Sen University in Guangzhou, China. He holds multiple patents in Automated and Integrated Testing.

Panelist 5

Yu Cao

Professor, Arizona State University

Biography:

Yu Cao received the B.S. degree in physics from Peking University and the Ph.D. degree in electrical engineering from University of California, Berkeley, in 1996 and 2002, respectively. He is now a Professor of Electrical Engineering at Arizona State University, Tempe, Arizona. He has published numerous articles and two books on nano-CMOS modeling and physical design. His research interests include brain-inspired computing, hardware design for on-chip learning, and reliable integration of nanoelectronics. He is the IEEE Fellow, for development of predictive technology models for reliable circuit and system integration.

Panelist 6

Ann Gui

Senior Engineering Manager, GM Cruise

Biography:

Ann has been in the semiconductor industry for more than 20 years. Currently she leads the silicon team at the autonomous vehicle company GM Cruise in San Francisco. Prior to that, she has led the development of many successful networking silicon products at Cortina System and Force10-Dell.

CASPA 2019 Dinner Banquet Performance

Jing Yang is a passionate violinist, enthusiastic musician, has performed for audiences throughout the United States, China and Singapore as a soloist at international major concert halls. She is a versatile musician both solo and ensemble and maintains an extensive repertoire, spanning from Baroque to the contemporary music.

Jing actively participates in competitions, performances. She was the first-place winner at the Stars of Tomorrow China National Competition in Beijing, was awarded the Woodruff Award for Excellence and received a full scholarship to attend Columbus State University’s Schwob School of Music, where her supervisor was Sergiu Schwartz. Jing’s awards also include second place prize at the US MTNA National String Competition in the Young Artist Category. She has worked with members of the Tokyo Quartet, Shanghai Quartet, Brentano Quartet and among others. Appearances as soloist and chamber musician include performances in Lincoln Center, New York; Woolsey Hall, New Haven CT; and Bill Theatre, Columbus, GA. Master class with Goto Midori, Cho-liang Lin, Shmuel Ashkenasi, Annie Kavafian and many others. During the years she studied with Prof. Schwartz, She won first place twice at the Intramural Concerto Competitions and was honored appeard as the soloist successfully collaborated with Maestro Juan R. Ramirez, Paul Hostetter and others all earned high praise. As an artist and orchestra performer, she has had the opportunity to collaborate with leading figures in the world of classical music, including Maestro Krzysztof Penderecki, John Adams, Peter Oundjian, Fred Cohen and among others. Jing was featured at the Bowdoin International Music festival. In the summer of 2015, she was invited as a soloist on a tour in mainland China and her performances earned rave reviews and has invited as a judge of United State International Music Competition violin category preliminary round.

Huan Yang, one of Chinese’s most talented pianist of his generation, passionate musician, active collaborative artist, and an intuitive teacher who delights music lovers and nurtures young people in major concert halls through eloquent live performances to help people rediscover the world of classical music. He is known for his musical insight, technical command, wide ranged repertoire. He has performed throughout United States, Mainland China, HongKong, Singapore and Philippines.

Huan began his piano studies at the age of eight and received award in many competitions, including the Third place at the China national piano competition in Beijing, the first prize of the Chinese contemporary music in Hong Kong, the first prize of the Unite State international music competition in San Francisco, And the global outstanding Chinese golden tripod award and etc. He had the honor of performing with venerable musicians such as Alexander Kobrin, Vijay Venkatesh, Ping Gao. As well as recitals and concerts at the world-renowned Weill Recital Hall at Carnegie Hall New York, Bill Theatre in Columbus, Tsuen wan town hall in Hong Kong, and China Wu Theater in Zhejiang and many others. “His performs very bright … His music is appealing.”-international daily news. As a pianist and chamber musician.

Huan was studied in the Music School and the Middle School of the Central Conservatory of Music in Beijing, and he received Woodruff Award full scholarship and B.A. degree in Schwob School of Music, Columbus State University, and he finished his graduate school from University of Southern California. He has had the privilege of studying with many other outstanding pianists, including Yuan Shen, Gila Goldstein, Alexanda Kobin Norman Krieger and Meng-Chieh Liu. Master classes with Jozef Stompel, Solomon Mikowsky, Jerome Lowenthal, Victor Rosenbaum, Ursula Oppens.

Joie Hua is currently the concert master of Orchestra Gradus ad Parnassum in the Bay Area and a 10th grade student. She began studying piano at age four and successfully completed 10 levels of the Certificate of Merit piano exams. At age ten, she picked up the violin and focused on mastering it. When entering 9th grade, she started to do home schooling to better manage her time for practicing violin.

Joie has performed solo in Santa Clara with Orchestra Gradus ad Parnassum and played at Carnegie Hall in New York. She is currently studying under Maestro Imant Airea.